# MC68000 EDUCATIONAL COMPUTER BOARD USER'S MANUAL

# IF YOU HAVE ANY QUESTIONS REGARDING THIS EDUCATIONAL MANUAL PLEASE CALL

MOTOROLA SPS

UNIVERSITY SUPPORT

432 NORTH 44TH STREET, SUITE 200

PHOENIX, AZ 85008

PH: (602) 302-8166

#### MC68000

#### EDUCATIONAL COMPUTER BOARD

#### USER'S MANUAL

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

EXORciser and EXORmacs are trademarks of Motorola Inc.

The computer program stored in the Read Only Memory of this device contains material copyrighted by Motorola Inc., first published 1981, and may be used only under a license such as the License For Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

#### WARNING

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND, IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTION MANUAL, MAY CAUSE INTERFERENCE TO RADIO COMMUNICATIONS. AS TEMPORARILY PERMITTED BY REGULATION, IT HAS NOT BEEN TESTED FOR COMPLIANCE WITH THE LIMITS FOR CLASS A COMPUTING DEVICES PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE, IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES MAY BE REQUIRED TO CORRECT THE INTERFERENCE.

Second Edition

Copyright 1982 by Motorola Inc.

First Edition January 1982

Dear Customer,

Congratulations on your recent purchase of the 68K Educational Computer Board.

#### YOUR MOTOROLA WARRANTY

Motorola Inc. warrants this product against defects in material and workmanship for a period of ninety (90) days from the original data of purchase. THIS WARRANTY EXTENDS TO THE ORIGINAL CUSTOMER ONLY AND IS IN LIEU OF ALL OTHER WARRANTIES, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS. In no event will the Seller be liable for any incidental or consequential damages.

During the warranty period, Motorola will replace, at no charge, components that fail, provided the product is returned (properly packed and shipped prepaid) to Motorola at the address printed below. Dated proof of purchase (such as a copy of the sales receipt or bill of sale) must be enclosed with shipment to validate warranty. We will return the shipment prepaid via UPS.\*

This warranty does not apply if, in the opinion of Motorola, the product has been damaged by accident, misuse, neglect, misapplication, or as a result of service or modification by other than the authorized Motorola Service Center referenced below.

#### AFTER-WARRANTY SERVICE

After your product is ninety (90) days old or warranty has been voided in any manner, you may return the product to us for repair. Please be sure to ship prepaid, properly pack the product, and include a certified check or money order for \$150.00 payable to Motorola Inc. Include any failure information you may have to help expedite repair time. We will return the shipment prepaid via UPS.\* We hope you will never need our repair, but it's nice to know you are protected anyway — and that help is nearby.

MOTOROLA C&E INC. Phoenix Service Depot 3332 E. Broadway Suite 102 Phoenix, Arizona 85040-2830 PH: 602-437-4331 FAX: 602-437-1858

\* FOR EXPEDITED RETURN SHIPMENTS, PLEASE INCLUDE AN ADDITIONAL \$20 IN YOUR PAYMENT. THIS CHARGE IS TO COVER AIR SHIPMENT. PRICES ARE SUBJECT TO CHANGE WITHOUT PRIOR NOTICE. PLEASE ENCLOSE A COPY OF THE ATTACHED PROBLEM REPORT WITH YOUR BOARD.

# PROBLEM REPORT

| NAME                                                                   |

|------------------------------------------------------------------------|

| COMPANY                                                                |

| ADDRESS                                                                |

| CITY, STATE, ZIP CODE                                                  |

| PHONE NUMBER                                                           |

| PLEASE FILL IN THE APPROPRIATE AREAS                                   |

| WARRANTY (90 DAYS FROM RECEIPT OF PRODUCT)                             |

| YES (BE SURE TO INCLUDE A COPY OF YOUR SALES RECEIPT)                  |

| NO (BE SURE TO INCLUDE A CERTIFIED CHECK OR MONEY ORDER FOR \$150.00*) |

| EXPEDITED SHIPPING                                                     |

| YES (BE SURE TO INCLUDE AN ADDITIONAL PAYMENT OF \$20.00*)             |

| TT NO                                                                  |

| APPLICATION INFORMATION                                                |

|                                                                        |

|                                                                        |

|                                                                        |

| FAILURE INFORMATION                                                    |

|                                                                        |

|                                                                        |

|                                                                        |

<sup>\*</sup> PRICES SUBJECT TO CHANGE WITHOUT NOTICE

|   |   |  |  | ٠. |

|---|---|--|--|----|

|   |   |  |  |    |

|   |   |  |  |    |

| 5 |   |  |  |    |

| • |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   | · |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

|   |   |  |  |    |

# TABLE OF CONTENTS

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 1                                                                                                                                                                                   | INTRODUCTION TO THE MC68000 EDUCATIONAL COMPUTER BOARD                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                      |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.3<br>1.4                                                                                                                       | WHAT IS THE MC68000 EDUCATIONAL COMPUTER BOARD?  GENERAL HARDWARE DESCRIPTION  System Memory  Serial Communications Ports  Programmable Timer  Parallel I/O Port (Printer Interface)  Audio Tape Interface  SYSTEM CONFIGURATIONS  SOFTWARE CAPABILITIES  SPECIFICATIONS                                                                                                                                                              | 1-3<br>1-4<br>1-4<br>1-4<br>1-6<br>1-6<br>1-6<br>1-6                                                                                 |

| CHAPTER 2                                                                                                                                                                                   | INSTALLATION AND POWER-UP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                      |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.2.1<br>2.2.2.2<br>2.2.3<br>2.2.4<br>2.2.4.1<br>2.2.4.2<br>2.3<br>2.3.1<br>2.3.2<br>2.4<br>2.5<br>2.5<br>2.5.1<br>2.5.2<br>2.5.2.2<br>2.5.2.1<br>2.5.2.2 | Checking System Clock Jumper Selecting Terminal Baud Rate Normal Operation - Transmitting and Receiving at the Same Baud Rate Special Operation - Transmitting and Receiving at Different Baud Rates SYSTEM HOOKUP INSTRUCTIONS Connecting the Terminal Connecting the Power Supplies SYSTEM TURN-ON AND INITIAL OPERATION PREPARATION FOR USE OF SYSTEM OPTIONS Printer Option Host Computer (Modem) Option Selecting Host Baud Rate | 2-3<br>2-5<br>2-5<br>2-5<br>2-7<br>2-7<br>2-8<br>2-8<br>2-10<br>2-11<br>2-13<br>2-14<br>2-16<br>2-16<br>2-18<br>2-18<br>2-20<br>2-21 |

| CHAPTER 3                                                                                                                                                                                   | USING THE MONITOR/DEBUG FIRMWARE                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                      |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.2.3<br>3.2.3                                                                                                                      | ABORT Button                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-3<br>3-4<br>3-4<br>3-5<br>3-5<br>3-5<br>3-5<br>3-6                                                                                 |

|                  |                                                         | Page |

|------------------|---------------------------------------------------------|------|

| 3.4              | COMMAND LINE FORMAT                                     | 3-6  |

| 3.4.1            | Expression as a Parameter                               | 3-7  |

| 3.4.2            | Address as a Parameter                                  | 3-7  |

| 3.4.2.1          | Address Formats                                         | 3-7  |

| 3.4.2.2          | Offset Registers                                        | 3–8  |

| 3.4.3            | Command Echo Back                                       | 3–8  |

| 3.5              | TUTOR COMMAND SET                                       | 3-9  |

| 3.5.1            | BF - Block of Memory Fill                               | 3-11 |

| 3.5.2            | BM - Block Move                                         | 3-12 |

| 3.5.3            | BR - Breakpoint                                         | 3-13 |

| 3.5.4            | BS - Block of Memory Search                             | 3-14 |

| 3.5.5            | BT - Block of Memory Test                               | 3-15 |

| 3.5.6            | DC - Data Conversion                                    | 3-16 |

| 3.5.7            | DF - Display Formatted Registers                        | 3-17 |

| 3.5.8            | DU - Dump Memory (in S-Record Format)                   | 3-18 |

| 3.5.9            |                                                         | 3-19 |

| 3.5.10           | GD - Go Direct Execute Program                          | 3-19 |

|                  | GO - Execute Program                                    | 3-20 |

| 3.5.11<br>3.5.12 | GT - Go Until Breakpoint                                | 3-21 |

|                  | HE - Help                                               |      |

| 3.5.13<br>3.5.14 | LO - Load (in S-Record Format)                          | 3-23 |

|                  | MD - Memory Display                                     | 3-24 |

| 3.5.15           | MM - Memory Modify                                      | 3-25 |

| 3.5.16           | MS - Memory Set                                         | 3-28 |

| 3.5.17           | NOBR - Remove Breakpoint                                | 3-29 |

| 3.5.18           | NOPA - Reset Printer Attach                             | 3-30 |

| 3.5.19           | OF - Offset                                             | 3-31 |

| 3.5.20           | PA - Printer Attach                                     | 3-32 |

| 3.5.21           | PF - Port Format                                        | 3-33 |

| 3.5.22           | .Rx - Individual Register Display/Change                | 3-35 |

| 3.5.23           | TM - Transparent Mode                                   | 3-36 |

| 3.5.24           | TR - Trace                                              | 3-38 |

| 3.5.25           | TT - Trace to Temporary Breakpoint                      |      |

| 3.5.26           | VE - Verify (in S-Record Format)                        | 3-40 |

| 3.6              | COMMAND SUMMARY AND MESSAGES                            | 3–41 |

| CHAPTER 4        | USING THE ASSEMBLER/DISASSEMBLER                        |      |

| 4 4              | TAMBADUATTAL                                            | 4 ^  |

| 4.1              | INTRODUCTION                                            | 4-3  |

| 4.1.1            | M68000 Assembly Language                                | 4-3  |

| 4.1.1.1          | Machine-Instruction Operation Codes                     |      |

| 4.1.1.2          | Directives                                              |      |

| 4.1.2            | Comparison with MC68000 Resident Structured Assembler . | 4-4  |

| 4.2              | SOURCE PROGRAM CODING                                   | 4-4  |

| 4.2.1            | Source Line Format                                      | 4-5  |

| 4.2.1.1          | Operation Field                                         | 4-5  |

| 4.2.1.2          | Operand Field                                           | 4-6  |

| 4.2.1.3          | Disassembled Source Line                                | 4-6  |

| 4.2.1.4          | Mnemonics and Delimiters                                | 4–6  |

| 4.2.1.5          | Character Set                                           | 4–8  |

| 4.2.2            | Instruction Summary                                     | 4-8  |

| 4.2.2.1          | Arithmetic Operations                                   | 4–8  |

| 4.2.2.2          | MOVE Instruction                                        | 4–9  |

|                  |                                                         |      |

\*

|                    |                                          | Page         |

|--------------------|------------------------------------------|--------------|

| 4.2.2.3            | Compare Instructions                     | 4-9          |

| 4.2.2.4            | Logical Operations                       | 4-10         |

| 4.2.2.5            | Shift Operations                         | 4-10         |

| 4.2.2.6            | Bit Operations                           | 4-11         |

| 4.2.2.7            | Conditional Operations                   | 4-11         |

| 4.2.2.8            | Branch Operations                        | 4-11         |

| 4.2.2.9            | Jump Operations                          | 4-12         |

| 4.2.2.10           | DBcc Instruction                         | 4-12         |

| 4.2.2.11           | Load/Store Multiple                      | 4-13         |

| 4.2.2.12           | Load Effective Address                   | 4-14         |

| 4.2.2.13           | Variants on Instruction Types            | 4-14         |

| 4.2.3              | Addressing Modes                         | 4-15         |

| 4.2.3.1            | Register Direct Modes                    | 4-18         |

| 4.2.3.2            | Memory Address Modes                     | 4-18         |

| 4.2.3.3            | Special Address Modes                    | 4-20         |

| 4.2.3.4            | Notes on Addressing Options              | 4-23         |

| 4.2.4              | DC.W Define Constant Directive           | 4-24         |

| 4.3                | ENTERING AND MODIFYING SOURCE PROGRAMS   | 4-24         |

| 4.3.1              | Invoking the Assembler/Disassembler      | 4-26         |

| 4.3.2              | Entering a Source Line                   | 4-26         |

| 4.3.3              | Program Entry/Branch and Jump Addresses  | 4-27         |

| 4.3.3.1            | Entering Absolute Addresses              | 4-27         |

| 4.3.3.2            | Desired Instruction Form                 | 4-28         |

| 4.3.3.3            | Current Location                         | 4-28         |

| 4.3.4              | Assembler Output/Program Listings        | 4-29         |

| 4.3.5              | Error Conditions and Messages            | 4-30         |

| 4.3.5.1            | Trap Errors                              | 4-30         |

| 4.3.5.2            | Improper Character                       | 4-31         |

| 4.3.5.3            | Number Too Large                         | 4-32         |

| 4.3.5.4            | Assembly Errors                          | 4-32         |

| 4.4                | TESTING/EXECUTING PROGRAMS               | 4-34         |

| 4.4.1              | System Initialization                    | 4-34         |

| 4.4.2              | Setting Breakpoints                      | 4-35         |

| 4.4.3              | Program Execution                        | 4-36         |

| 4.4.4              | Trace Mode                               | 4-37         |

| 4.4.5              | Inserting and Deleting Source Lines      | 4-39         |

| 4.5                | SAVING PROGRAMS                          | 4-42<br>4-42 |

| 4.5.1<br>4.5.2     | Saving Programs on Tape                  | 4-42         |

| 4.5.2              | Loading and Verifying Programs from Tape | 4-43         |

|                    | Upload to a Host                         | 4-45         |

| 4.5.3.1<br>4.5.3.2 | EXORmacs as Host                         | 4-45         |

| 4.5.4              | Download from a Host                     | 4-47         |

| 4.5.4.1            | EXORciser as Host                        | 4-47         |

| 4.5.4.2            | EXORmacs as Host                         | 4-47         |

| エチン・エ・ム            |                                          | 2 2/         |

|           | the state of contents (contents)                     | Page         |

|-----------|------------------------------------------------------|--------------|

| CHAPTER 5 | TRAP 14 HANDLER                                      |              |

| 5.1       | WHAT IS THE TRAP 14 HANDLER?                         | 5-3          |

| 5.1.1     | Types of Exceptions                                  | 5-3          |

| 5.1.2     | MC68000 Exception Processing                         | 5-3          |

| 5.1.3     | Trap 14 Handler                                      | 5-4          |

| 5.2       | TRAP 14 CALLING SEQUENCE                             | 5-4          |

| 5.3       | TRAP 14 FUNCTIONS                                    | 5-6          |

| 5.3.1     | Input/Output Functions                               | 5-6          |

| 5.3.2     | Conversion Functions                                 | 5 <b>-</b> 9 |

| 5.3.3     | Buffer Control Functions                             | 5-10         |

| 5.3.4     | Transfer Control to TUTOR                            | 5-12         |

| 5.3.5     | Inserting Additional Functions                       | 5-13         |

| CHAPTER 6 | SYSTEM INPUT/OUTPUT                                  |              |

| 6.1       | INTRODUCTION - INPUT/OUTPUT LSI DEVICES              | 6 3          |

| 6.1.1     | MC6850 Asynchronous Communications Interface Adapter | 6–3          |

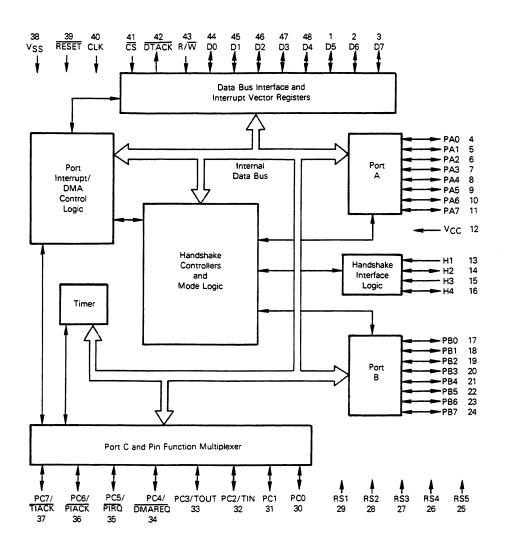

| 6.1.2     | MC68230 Parallel Interface and Timer                 | 6-3          |

| 6.1.3     | I/O Device Address Map                               | 6-5          |

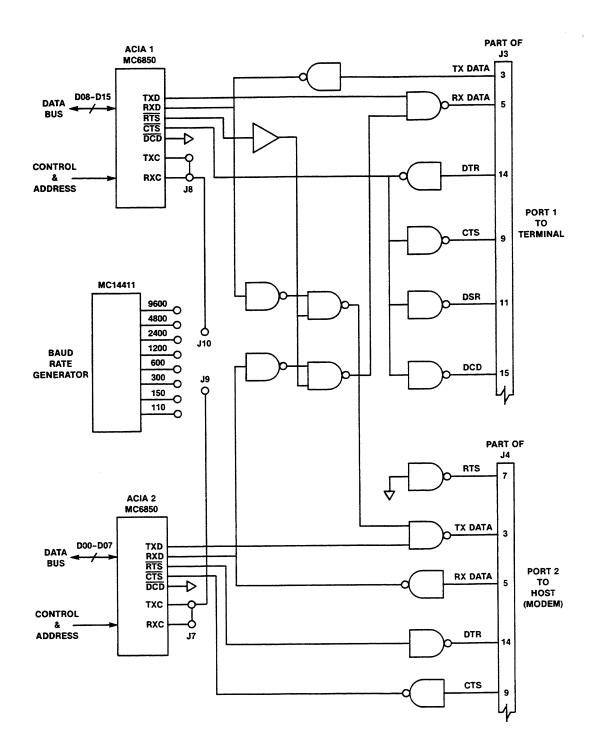

| 6.2       | SERIAL COMMUNICATIONS - PORT 1 AND PORT 2            | 6-7          |

| 6.2.1     | ACTA Control Dogistor                                | 6-10<br>6-10 |

| 6.2.2     | ACIA Control Register                                |              |

| 6.2.3     | Baud Rates                                           | 6-12         |

| 6.2.4     | TUTOR Firmware I/O Drivers                           | 6-13         |

| 6.2.5     | Port 1 Terminal Interface                            | 6-13         |

| 6.2.6     | Port 2 Host Interface                                | 6-14         |

|           | Transparent Mode                                     | 6-14         |

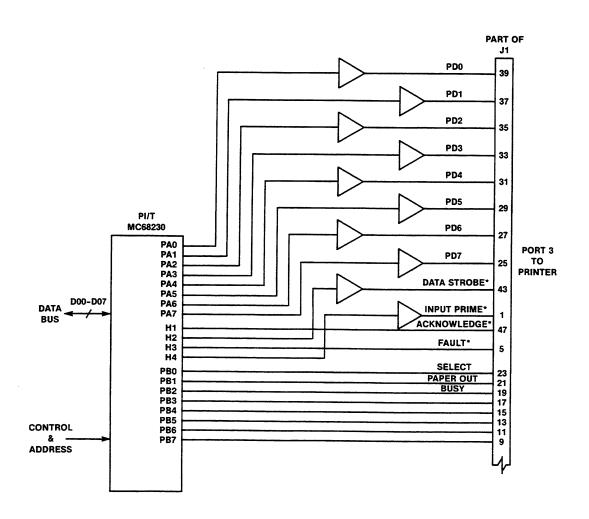

| 6.3       | PARALLEL I/O PORT 3 - PRINTER INTERFACE              | 6-15         |

| 6.3.1     | Signal Line Configuration                            | 6-15         |

| 6.3.2     | Programming the PI/T                                 | 6–17         |

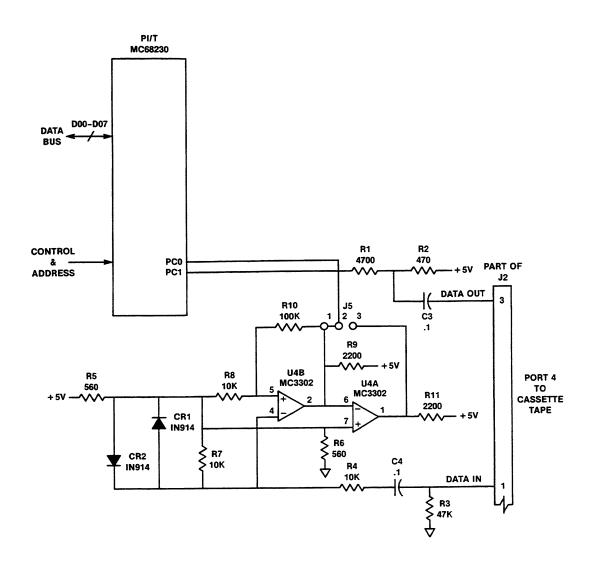

| 6.4       | AUDIO TAPE INTERFACE - PORT 4                        | 6–19         |

| 6.4.1     | Data Transfer Baud Rate                              | 6–19         |

| 6.4.2     | Circuit Operation                                    | 6–19         |

| 6.4.3     | Selecting Noninverted Data                           | 6–21         |

| 6.4.4     | Programming the PI/T                                 | 6-22         |

| 6.5       | PI/T TIMER                                           | 6-22         |

| 6.6       | SYSTEM INTERRUPTS                                    | 6–23         |

| 6.6.1     | MC68000 Interrupt Structure                          | 6-24         |

| 6.6.2     | Interrupt Software Routines                          | 6–26         |

| CHAPTER 7 | HARDWARE DESCRIPTION                                 |              |

| 7.1       | INTRODUCTION                                         | 7-3          |

| 7.2       | FUNCTIONAL DESCRIPTION                               | 7-3          |

| 7.2.1     | MC68000L4 Microprocessor                             | 7-3          |

| 7.2.2     | Address Decode                                       | 7-3          |

| 7.2.3     | 32K Byte RAM                                         | 7-5          |

| 7.2.4     | 16K Byte ROM                                         | 7-5          |

| 7.2.5     | Serial Communications Ports                          | 7-5          |

| 7.2.6     | MC68230 PI/T (Printer Interface, Cassette Tape       |              |

|           | Interface, and Timer)                                | 7-6          |

5

|                                                                                         |                                                                                                                   | Page                                   |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 7.2.7 7.2.8 7.2.9 7.2.10 7.2.11 7.3 7.3.1 7.3.2 7.3.3 7.3.4 7.3.5 7.3.6 7.3.6.1 7.3.6.2 | •••••                                                                                                             | 7-6<br>7-6<br>7-7<br>7-7<br>7-7<br>7-7 |

| CHAPTER 8                                                                               | SUPPORT INFORMATION                                                                                               |                                        |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                         | INTRODUCTION  CONNECTOR SIGNAL DESCRIPTIONS  JUMPER HEADER, CONNECTOR, AND SWITCH LOCATIONS  PARTS LIST  DIAGRAMS | 8 <del>-</del> 3<br>8-3<br>8-3         |

| APPENDIX A<br>APPENDIX B<br>APPENDIX C                                                  | S-RECORD OUTPUT FORMAT                                                                                            |                                        |

# LIST OF ILLUSTRATIONS

|        |                      |                                                                                                                | Page              |

|--------|----------------------|----------------------------------------------------------------------------------------------------------------|-------------------|

| FIGURE | 1-1.<br>1-2.<br>1-3. | MC68000 Educational Computer Board                                                                             | 1-2<br>1-5<br>1-7 |

|        | 2-1.<br>2-2.         | MEX68KECB Board Layout                                                                                         | 2-4<br>2-6        |

|        | 2-3.                 | Detail Showing Location of Holes J12, J13, J14, J15 to Connect Discrete Power Wires                            | 2-7               |

|        | 2-4.                 | Interconnection Diagram for Baud Rate Selection                                                                | 2-8               |

|        | 2-5.<br>2-6.         | Terminal Baud Rate Select Jumper (J10)                                                                         | 2-9<br>2-11       |

|        | 2-7.<br>2-8.         | Terminal Cable Detail and Signal Line Connections Terminal Cable Connection to MEX68KECB                       | 2-12<br>2-13      |

|        | 2-9.<br>2-10.        | Expanded System Configuration with Options                                                                     | 2-15<br>2-17      |

|        | 2-11.<br>2-12.       | Printer Cable Connection to MEX68KECB                                                                          | 2-18<br>2-19      |

|        | 2-13.                | Host Cable Signal Line Connections                                                                             | 2-20              |

|        |                      | Host Computer Cable Connection to MEX68KECB                                                                    | 2-21<br>2-22      |

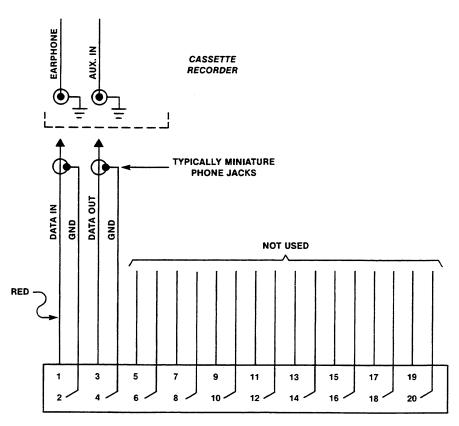

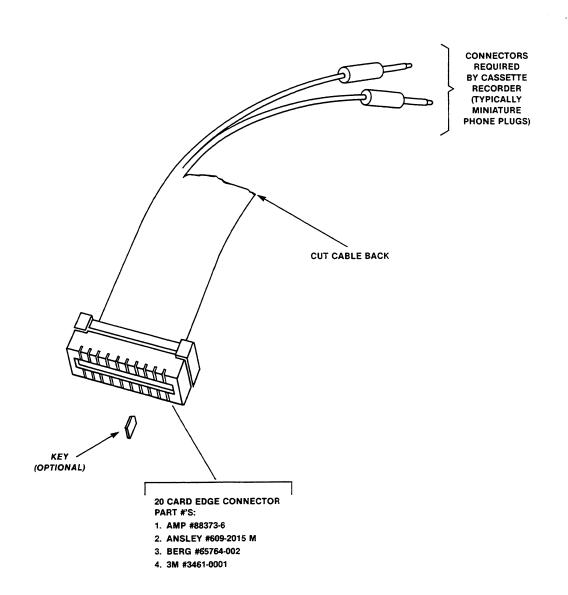

|        | 2-15B.<br>2-16.      | Cassette Recorder Cable Detail                                                                                 | 2-23<br>2-24      |

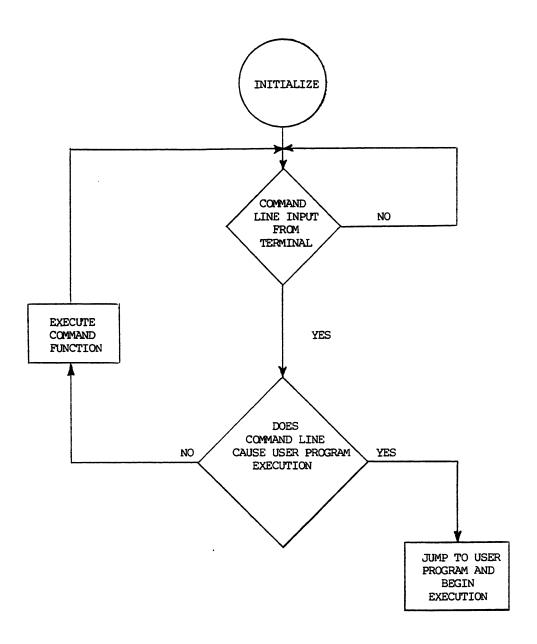

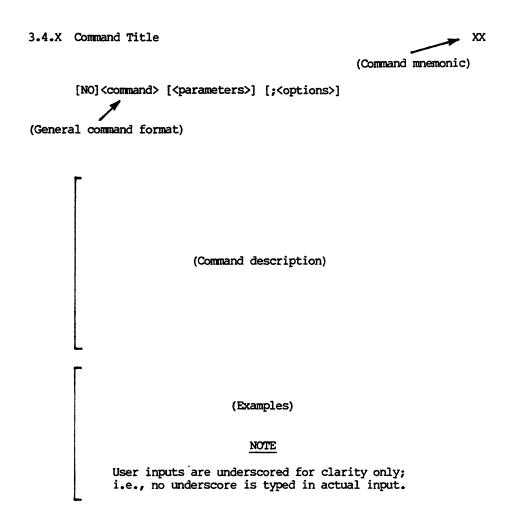

|        | 3-1.<br>3-2.         | Flow Diagram of TUTOR Operational Mode                                                                         | 3-2<br>3-10       |

|        | 4-1.                 | Example Program to Convert ASCII Digit to Hexadecimal Value                                                    | 4-25              |

|        | 4-2.<br>4-3.         | ASCII Character Set Example Program as Entered into Educational Computer                                       | 4-25<br>4-29      |

|        | 4-4.                 | Example Program Listing                                                                                        | 4-29              |

|        | 4-5.<br>4-6.         | Examples of Trap Errors                                                                                        |                   |

|        | 4-7.<br>4-8.         | Example of a Number which is Too Large<br>Examples of Assembly Errors                                          | 4-32<br>4-33      |

|        | 4-9.                 | Initializing Registers and Setting Breakpoint for Example Program                                              | 4-35              |

|        | 4-10.<br>4-11.       | Execution of Example Program                                                                                   | 4-36<br>4-37      |

|        | 4-12.<br>4-13.       | Inserting Missing Source Line into Example Program Corrected Example Program Listing                           |                   |

|        | 6-1.<br>6-2.         | System I/O Block Diagram                                                                                       | 6-2               |

|        | 6-3.                 | MC68230 PI/T Block Diagram                                                                                     | 6-6               |

|        | 6-4.<br>6-5.         | Serial Communications Ports Functional Schematic Diagram Printer Interface Port 3 Functional Schematic Diagram | 6-11<br>6-16      |

|        | 6-6.<br>6-7.         | Audio Tape Interface                                                                                           | 6-20<br>6-21      |

|        | 6-8                  | Address Translated from 8-Bit Vector Number                                                                    | 6-26              |

5

#### LIST OF ILLUSTRATIONS (cont'd)

|                                                          | LIST OF TELOSTRATIONS (COIL U)                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

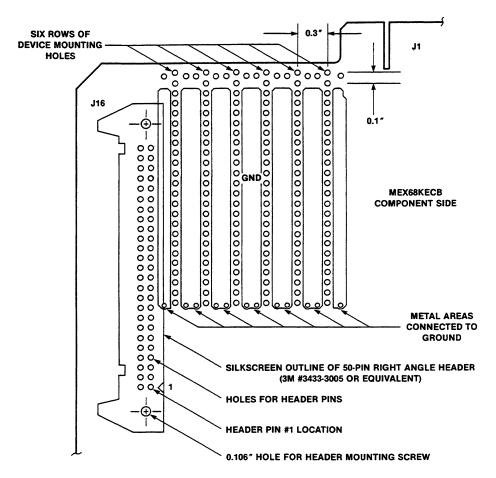

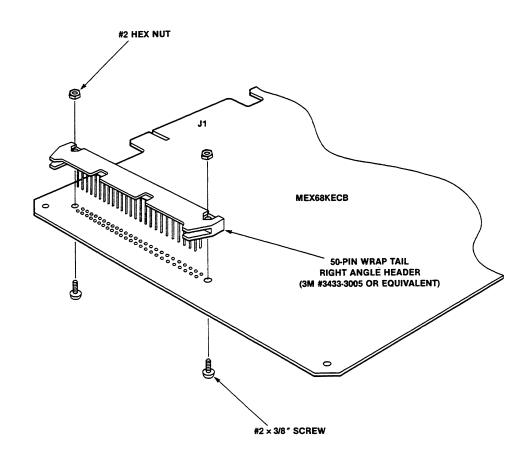

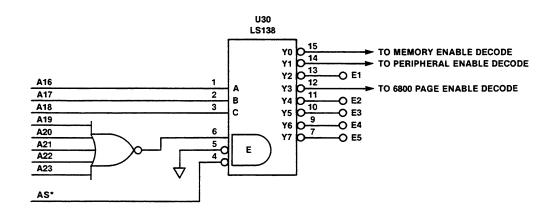

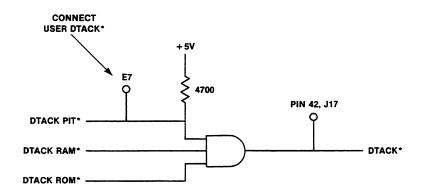

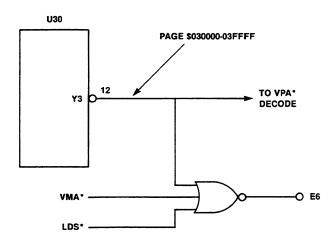

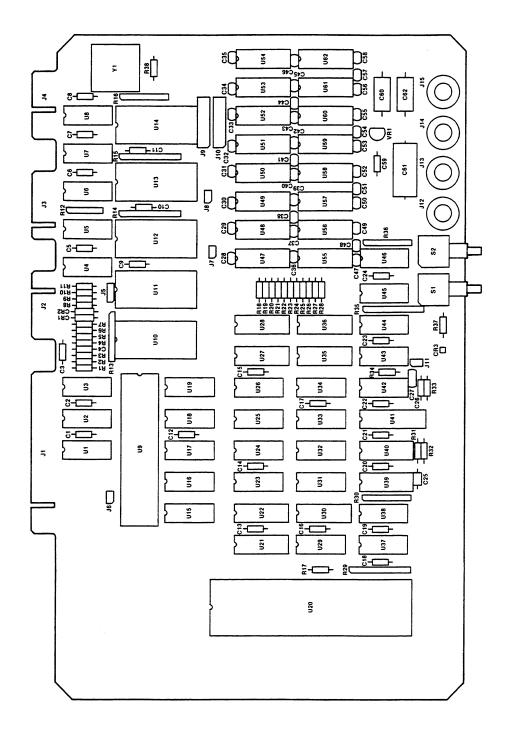

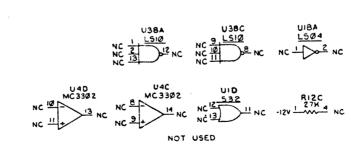

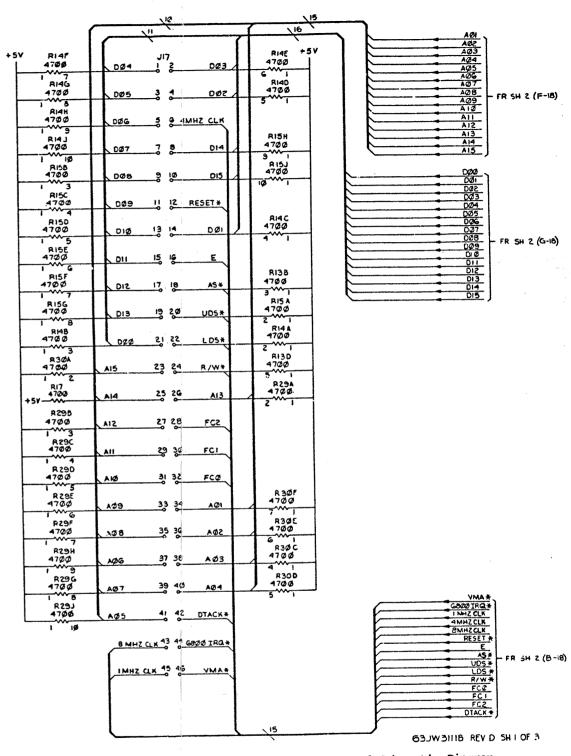

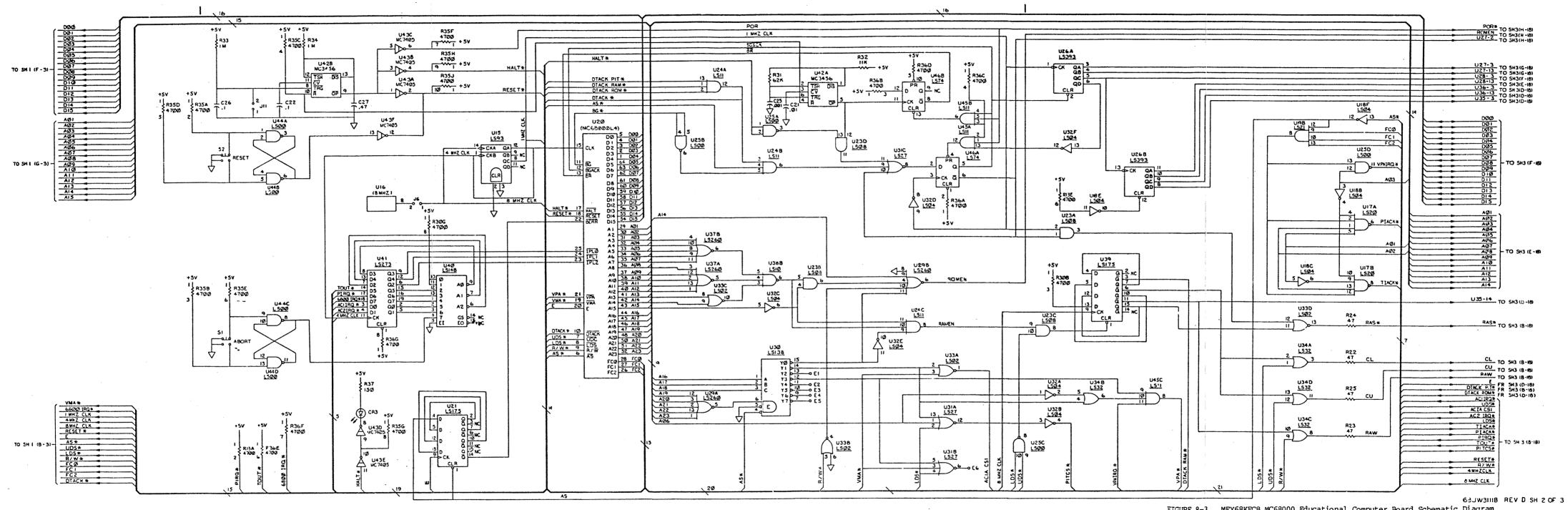

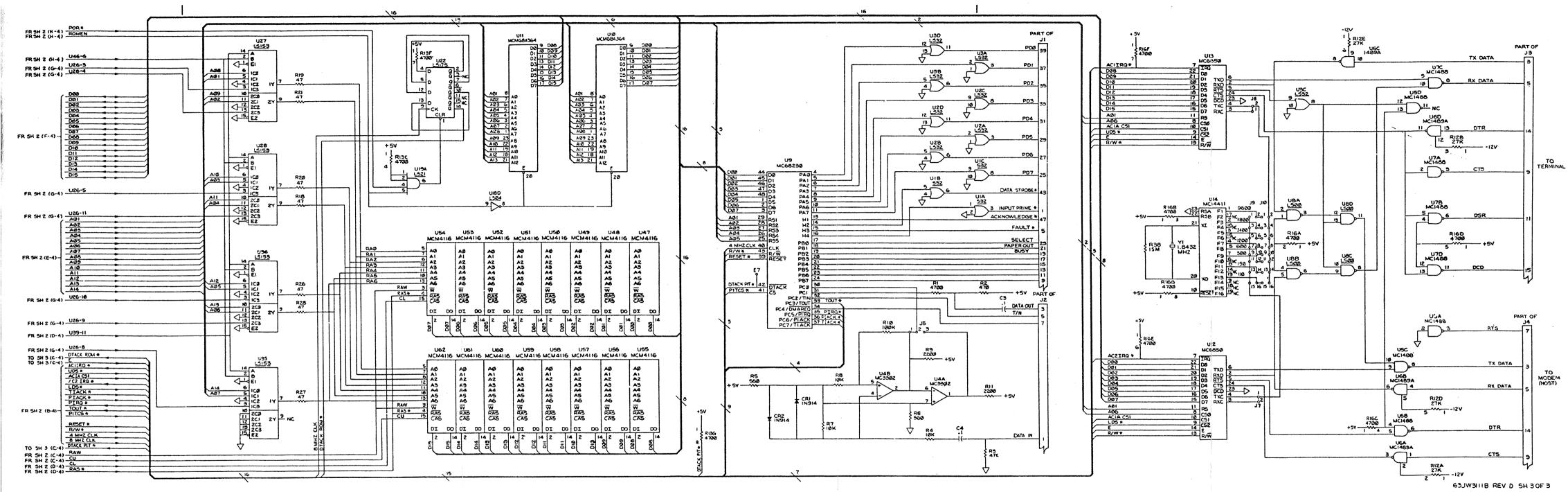

| FIGURE 7-1. 7-2. 7-3. 7-4. 7-5. 7-6. 7-7. 8-1. 8-2. 8-3. | Block Diagram - Educational Computer Board  MEX68KECB Signal Connection Points For Wire-Wrap  Detail of Wire-Wrap Area  Auxiliary I/O Header Mounting Detail  Address Decode Logic For Memory Map Primary Segments  DTACK* Signal Generation  M6800 Page Address Signal Generation  MEX68KECB Header, Connector, and Switch Locations  MEX68KECB Parts Location Diagram  MEX68KECB MC68000 Educational Computer Board  Schematic Diagram |      |

|                                                          | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| TABLE 1-1.                                               | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-9  |

| 2-1.                                                     | Headers J9 and J10 Jumpers to Select Serial Port Baud Rates                                                                                                                                                                                                                                                                                                                                                                              | 2-9  |

| 3-1.                                                     | TUTOR Commands                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-9  |

| 3-2.                                                     | TUTOR Commands and Options                                                                                                                                                                                                                                                                                                                                                                                                               | 3-41 |

| 3-3.                                                     | Error Messages and Other Messages                                                                                                                                                                                                                                                                                                                                                                                                        | 3-43 |

| 4-1.                                                     | Address Modes                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-16 |

| 5-1.                                                     | TRAP 14 Function Summary                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-5  |

| 5-2.                                                     | Input Functions                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-8  |

| 5-3.                                                     | Output Functions                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-8  |

| 5-4.                                                     | Hex Conversion Routines                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-10 |

| 5-5.                                                     | ASCII Conversion Routines                                                                                                                                                                                                                                                                                                                                                                                                                | 5-11 |

| 5 <del>-</del> 6.                                        | Buffer Control Functions                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-11 |

| 5-7.                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-12 |

| 5-7.<br>5-8.                                             | Transfer Control to TUTOR                                                                                                                                                                                                                                                                                                                                                                                                                | 5-14 |

|                                                          | Inserting Additional Functions                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 6-1.                                                     | MC68230 PI/T Address Map                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-8  |

| 6-2.                                                     | MC6850 ACIA Address Map                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-9  |

| 6-3.                                                     | ACIA Control Register Bits                                                                                                                                                                                                                                                                                                                                                                                                               | 6-12 |

| 6-4.                                                     | PI/T Registers Used in Printer Interface                                                                                                                                                                                                                                                                                                                                                                                                 | 6-18 |

| 6-5.                                                     | Interrupt Priority Levels                                                                                                                                                                                                                                                                                                                                                                                                                | 6-25 |

| 7-1.                                                     | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-4  |

| 7-2.                                                     | J17 Signal Designations                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-12 |

| 7-3.                                                     | Address Segment Enable Sigals for Wire-Wrap Users                                                                                                                                                                                                                                                                                                                                                                                        | 7-13 |

| 8-1.                                                     | Connector Jl Printer Port 3 Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                              | 8-4  |

| 8-2.                                                     | Connector J2 Audio Cassette Tape Interface                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                                                          | Port 4 Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                   | 8-5  |

| 8-3.                                                     | Connector J3 Serial Communications Port 1                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                                          | (To Terminal) Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                            | 8–6  |

| 8-4.                                                     | Connector J4 Serial Communications Port 2                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 0 4.                                                     | (To Host/Modem) Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                          | 8-6  |

| 8-5.                                                     | MEX68KECB Connector and Header Manual References                                                                                                                                                                                                                                                                                                                                                                                         | 8-7  |

| 8 <del>-</del> 6.                                        | MEX68KECB Parts List                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| o-o.                                                     | PEADORELD FAILS LIST                                                                                                                                                                                                                                                                                                                                                                                                                     | 0-0  |

| 5 |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

#### CHAPTER 1

# INTRODUCTION TO THE MC68000 EDUCATIONAL COMPUTER BOARD

The purpose of this manual is to provide the user with a comprehensive guide for understanding and utilizing the MC68000 Educational Computer Board. The computer board is intended primarily as a self-supporting means for evaluating and learning about the MC68000 16-bit microprocessor. Chapter 1 contains information describing the board and its system configuration.

|       |                                                 | Page |

|-------|-------------------------------------------------|------|

| 1.1   | WHAT IS THE MC68000 EDUCATIONAL COMPUTER BOARD? | 1-3  |

| 1.2   | GENERAL HARDWARE DESCRIPTION                    | 1-4  |

| 1.2.1 | System Memory                                   | 1-4  |

| 1.2.2 | Serial Communications Ports                     | 1-4  |

| 1.2.3 | Programmable Timer                              | 1-4  |

| 1.2.4 | Parallel I/O Port (Printer Interface)           | 1–6  |

| 1.2.5 | Audio Tape Interface                            | 1-6  |

| 1.3   | SYSTEM CONFIGURATIONS                           | 1–6  |

| 1.4   | SOFTWARE CAPABILITIES                           | 1-6  |

| 1.5   | SPECIFICATIONS                                  | 1-8  |

FIGURE 1-1. MC68000 Educational Computer Board

#### CHAPTER 1

#### INTRODUCTION TO THE MC68000 EDUCATIONAL COMPUTER BOARD

# 1.1 WHAT IS THE MC68000 EDUCATIONAL COMPUTER BOARD?

Intended primarily for training and educational use, including college-level courses and industrial in-plant training, the MC68000 Educational Computer Board (ECB) serves as an economical yet comprehensive introduction to systems based on the M68000 family of microcomputer products. Located on a single small printed circuit (PC) card (Figure 1-1), a complete microprocessor system is provided, including an MC68000 16-bit microprocessor, memory, parallel input/output (I/O), and serial communications I/O. The user must only connect an RS-232C-compatible "dumb" terminal and power supplies to have a functional system.

For ease-of-use, the ECB has a resident firmware package that provides a self-contained programming and operating environment. The firmware, aptly named "TUTOR", provides the user with monitor/debug, assembly/disassembly, program entry, and I/O control functions. Utilizing the capabilities provided by the system, the user can investigate and learn the computing power and architectural features of the MC68000. This system also provides a working example of the microprocessor external bus structure and interface to memory and peripheral devices.

The Educational Computer Board's features include:

- a. 4-megahertz MC68000 16-bit MPU.

- b. 32K bytes of dynamic RAM (DRAM) arranged as  $16K \times 16$ .

- c. 16K-byte firmware ROM/EPROM monitor addressed as 8K x 16.

- d. Two serial communication ports provided for a terminal and a host. Both are RS-232C-compatible and have selectable baud rates.

- e. Programs can be downloaded from or uploaded to a host system.

- f. A parallel port (16 data lines with handshake) can be used for I/O or for a Centronics-compatible printer interface.

- g. Audio tape serial I/O port.

- h. Self-contained operating firmware that provides monitor, debug, and disassembly/assembly functions.

- i. 24-bit programmable timer.

- j. Wire-wrap area provided for custom circuitry.

- k. RESET and ABORT function switches.

#### 1.2 GENERAL HARDWARE DESCRIPTION

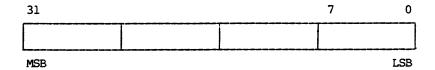

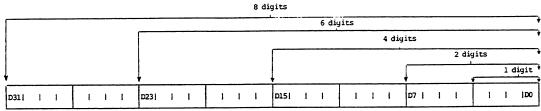

The MC68000 Educational Computer Board provides the RAM, ROM, timer, and I/O necessary for learning and evaluating the attributes of the MC68000. This microprocessor has a 16-bit data bus and a 23-bit address bus (A1-A23). The address bus is, in effect, 24 bits and provides a memory addressing range of 16 megabytes. The processor also has eight 32-bit data registers, seven 32-bit address registers, two 32-bit stack pointers, a 32-bit program counter, and a 16-bit status register. The MC68000 Data Sheet and User's Manual (MC68000UM), which are included in the ECB's documentation, describe the device in detail.

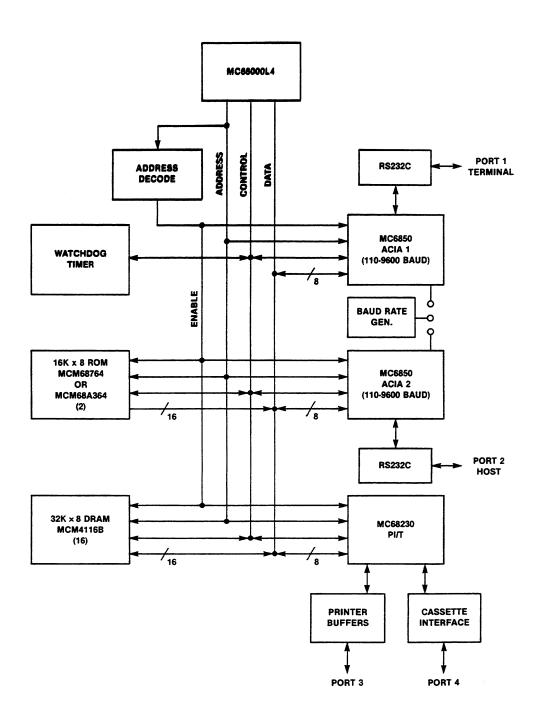

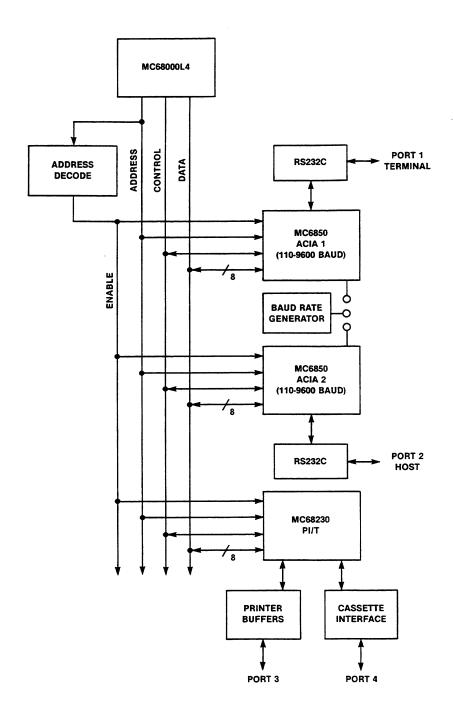

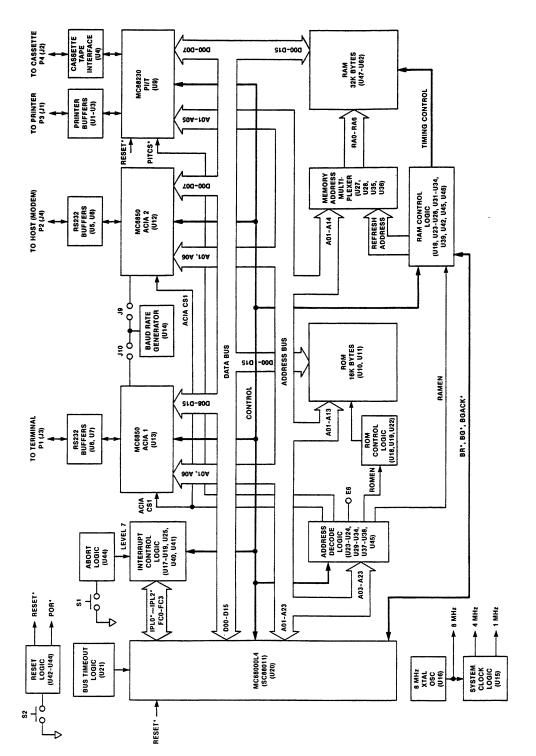

A 4-MHz MC68000 MPU is used on the educational board (a functional block diagram is shown in Figure 1-2). All the memory and I/O devices communicate with the MPU via a common parallel bus. The various functional areas of the board are described briefly in the following paragraphs.

#### 1.2.1 System Memory

The system memory consists of 32K bytes of dynamic RAM and 16K bytes of ROM or EPROM (two 8-bit bytes = 1 word). The RAM is used both for scratchpad space for the TUTOR firmware and for user programs. Approximately 2K bytes are reserved for the monitor scratchpad; the remaining RAM (approximately 30K bytes) is available to the user. The system firmware occupies the 16K-byte read-only memory.

#### 1.2.2 Serial Communications Ports

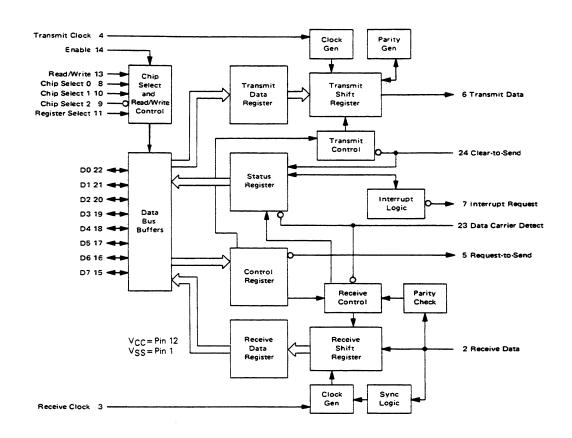

Two asynchronous serial communication ports, designated Port 1 for the Terminal and Port 2 for the Host, are provided on the board. Both of these ports are RS-232C-compatible (an E.I.A. standard). The terminal that provides user interface is connected to the educational computer via Port 1, and Port 2 can be connected to a modem or directly to a host computer. The host computer can be used to provide more powerful software capabilities such as program assembly, file management, and editing, and for downloading or uploading programs. Also, an operational condition called transparent mode can be used on the MEX68KECB. This transparent mode effectively bypasses the board and allows the terminal to communicate directly with the host. The terminal and host baud rates must be the same for this mode.

Both serial ports can be jumpered for various data transmission rates (110-9600 baud). Also, if required, either port can be modified to transmit and receive at different baud rates.

#### 1.2.3 Programmable Timer

Contained within the MC68230 PI/T device is a 24-bit general purpose timer. The timer is a synchronous counter that can be used for generating or measuring both time delays and various frequencies. The timer can be clocked by a 5-bit prescaler or directly, and the clock source can be the 4-MHz system clock or an external clock.

FIGURE 1-2. Functional Block Diagram

FIGURE 1-3. System Configurations

An assembly listing of the TUTOR firmware, excluding the interactive assembler and disassembler modules, can be purchased from Motorola under the part number M68KTUTOR. Machine-readable source for all the modules can be purchased under part numbers:

M68KTUTORS - VERSAdos 8" floppy diskette M68KTUTORT - VERSAdos hard disk cartridge

For program development, an interactive assembler/editor function is used in which the source program is not saved. Each instruction is translated into the proper object code and is stored in memory on a line-by-line basis at the time of entry. The assembler source statement is composed of operation and operand fields; line numbers, labels, and comments are not allowed.

In order to display an instruction, the firmware disassembles the object code and displays the instruction mnemonic and operands. Editing is done by re-entering a source statement.

If higher-level assembly capabilities are required, a macro assembler or cross assembler can be run on a host computer. Data can be uploaded and downloaded to the host via serial Port 2.

#### 1.5 SPECIFICATIONS

Table 1-1 lists basic specifications for the MC68000 Educational Computer Board (MEX68KECB).

TABLE 1-1. Specifications

| Microprocessor                  | MC68000 (4 MHz)                                                                                                                                   |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Input/Output                    |                                                                                                                                                   |

| Parallel I/O                    | MC68230 (16 data lines, 4 control lines) normally configured as Centronics-type printer interface. 24-bit programmable timer included in MC68230. |

| Cassette Interface              | 1300 baud serial audio tape.                                                                                                                      |

| Serial I/O Ports                | Two — one terminal and one host (modem).                                                                                                          |

| Interface                       | RS-232C interface.                                                                                                                                |

| Baud rate                       | Strap selectable: 110, 150, 300, 600, 1200, 2400 4800, 9600.                                                                                      |

| System clock                    | 8-MHz crystal providing 4-MHz processor operation.                                                                                                |

| Memory                          | 32K bytes RAM<br>16K bytes ROM                                                                                                                    |

| Power requirements<br>(Typical) | +5.0 V/750 mA, +12 V/50 mA, -12 V/50 mA                                                                                                           |

| Operating temperature           | 0 to 50° C                                                                                                                                        |

| Board Dimensions (Approx.)      |                                                                                                                                                   |

| LxWxH                           | 7.5 in. x 10.5 in. x 1.5 in.<br>(19 cm x 27 cm x 4 cm)                                                                                            |

|     |  | • |

|-----|--|---|

|     |  |   |

|     |  |   |

| A   |  |   |

| £ . |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

|     |  |   |

#### CHAPTER 2

#### INSTALLATION AND POWER-UP INSTRUCTIONS

This chapter provides unpacking, preparation—for—use, installation, and power—up instructions for the MEX68KECB. The board has been designed to require a minimum of hardware modifications; however, the proper serial port baud rates must be selected and the proper cables used to ensure trouble—free start—up. Please read and follow the instructions in this chapter to provide quick start—up and to avoid possible damage to the board.

|         |                                                                        | Page |

|---------|------------------------------------------------------------------------|------|

| 2.1     | UNPACKING INSTRUCTIONS                                                 | 2-3  |

| 2.2     | PREPARING THE BOARD FOR USE                                            | 2-5  |

| 2.2.1   | Attaching Standoff Legs                                                | 2-5  |

| 2.2.2   | Providing Power to the Board                                           | 2-5  |

| 2.2.2.1 | Banana Jacks                                                           | 2-5  |

| 2.2.2.2 | Alternate Method - Discrete Wires                                      | 2-7  |

| 2.2.3   | Checking System Clock Jumper                                           | 2-7  |

| 2.2.4   | Selecting Terminal Baud Rate                                           | 2-8  |

| 2.2.4.1 | Normal Operation - Transmitting and Receiving at the Same Baud Rate    | 2-8  |

| 2.2.4.2 | Special Operation - Transmitting and Receiving at Different Baud Rates | 2-10 |

| 2.3     | SYSTEM HOOKUP INSTRUCTIONS                                             | 2-11 |

| 2.3.1   | Connecting the Terminal                                                | 2-13 |

| 2.3.2   | Connecting the Power Supplies                                          | 2-14 |

| 2.4     | SYSTEM TURN-ON AND INITIAL OPERATION                                   | 2-14 |

| 2.5     | PREPARATION FOR USE OF SYSTEM OPTIONS                                  | 2-16 |

| 2.5.1   | Printer Option                                                         | 2-16 |

| 2.5.2   | Host Computer (Modem) Option                                           | 2-18 |

| 2.5.2.1 | Selecting Host Baud Rate                                               | 2-18 |

| 2.5.2.2 | Cable Connection                                                       | 2-20 |

| 2.5.3   | Audio Cassette Option                                                  | 2-21 |

. 3

#### CHAPTER 2

# INSTALLATION AND POWER-UP INSTRUCTIONS

#### 2.1 UNPACKING INSTRUCTIONS

#### NOTE

If shipping carton is damaged on receipt, request carrier's agent be present during unpacking and inspection of the module.

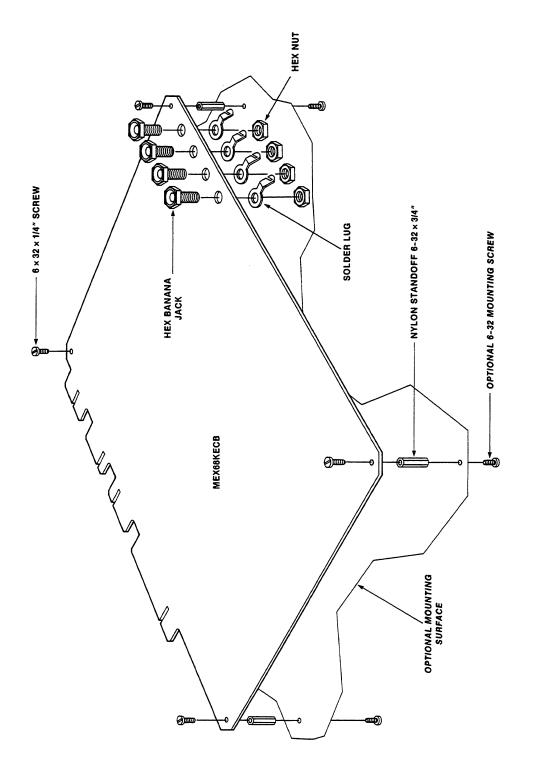

Unpack the computer board from its shipping carton. Save the packing material for storing or reshipping the board. Refer to the packing list and verify that all items are present. As shipped, the MEX68KECB includes:

- a. MEX68KECB Educational Computer Board

- b. Four 6-32x1/4" screws

- c. Four threaded 6-32x3/4" nylon standoffs

- d. Four banana jacks (including hex nuts and solder lugs)

- e. Seven plastic cap jumpers

After verifying that items (including any optional parts) are present, inspect the board for damage. Ensure that there are no broken, damaged, or missing parts, and that there is no physical damage to the printed circuit board.

#### CAUTION

WHEN HANDLING THE BOARD, AVOID TOUCHING AREAS OF MOS CIRCUITRY; STATIC DISCHARGE CAN DAMAGE INTEGRATED CIRCUITS.

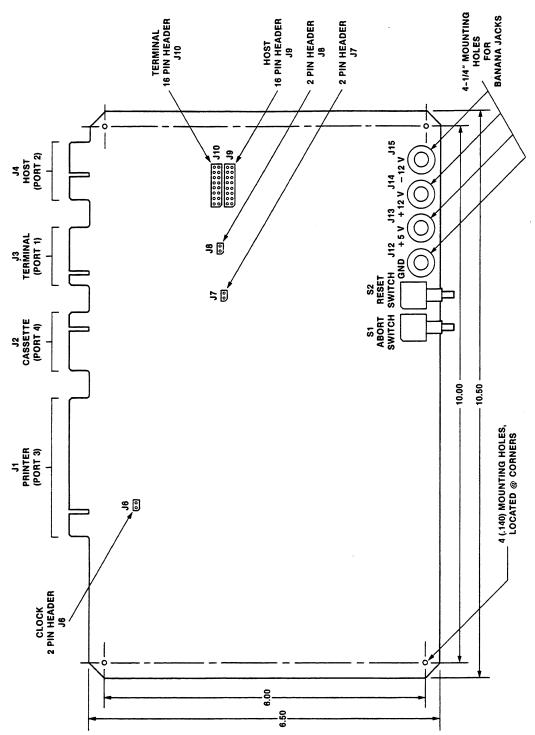

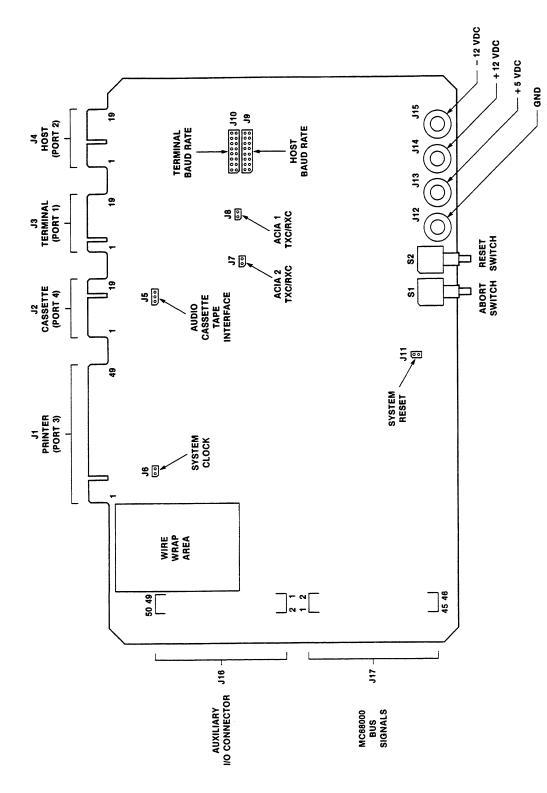

FIGURE 2-1. MEX68KECB Board Layout

#### 2.2 PREPARING THE BOARD FOR USE

The MEX68KECB is intended primarily for training and educational use, including college-level courses and industrial in-plant training. In its most simple configuration, the board requires only an RS-232C compatible terminal (plus cable) and power supplies to function. The preparation instructions are intended to set up the board for this configuration. Use of optional features (audio cassette, host, or printer) requires additional preparation, which is covered in other sections of this chapter.

Figure 2-1 shows a layout of the MEX68KECB. Board preparation concerns the following items:

- a. Because the board is intended for laboratory use, standoff legs can be used to allow the board to set on a bench.

- b. Power connections must be made. Banana jacks can be used or wires can be soldered to the board.

- c. Check that the system clock jumper (J6) is in place.

- d. The terminal baud rate must be selected.

#### 2.2.1 Attaching Standoff Legs

Four holes located at the corners of the board are used to mount the nylon standoffs. These are screwed to the back side (opposite of component side) of the card, as shown in Figure 2-2.

#### NOTE

The user may choose to mount the module on or in an enclosure via these holes. Dimensions are shown in Figure 2-1. The nylon standoffs can be used as spacers to provide clearance of 3/4 inch needed by the banana jacks.

#### 2.2.2 Providing Power to the Board

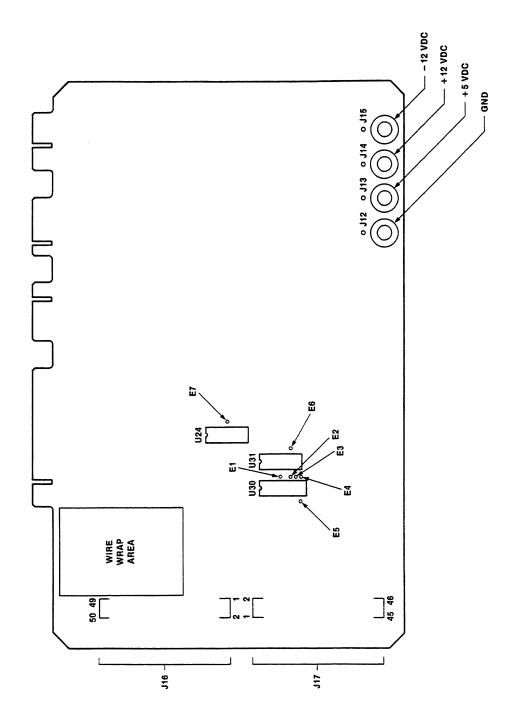

2.2.2.1 <u>Banana Jacks</u>. Four banana jacks compatible with standard banana plugs are provided for power connectors (+12 Vdc, +5 Vdc, Ground, -12 Vdc). These are mounted in four 1/4-inch holes at a corner of the board, as shown in Figure 2-2.

3

FIGURE 2-2. Hardware Mounting Detail

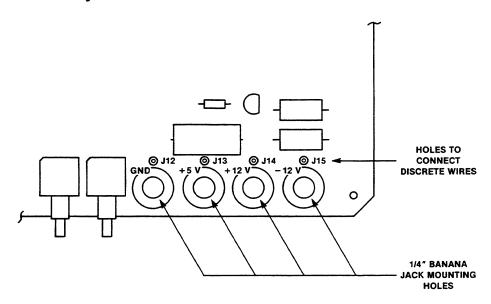

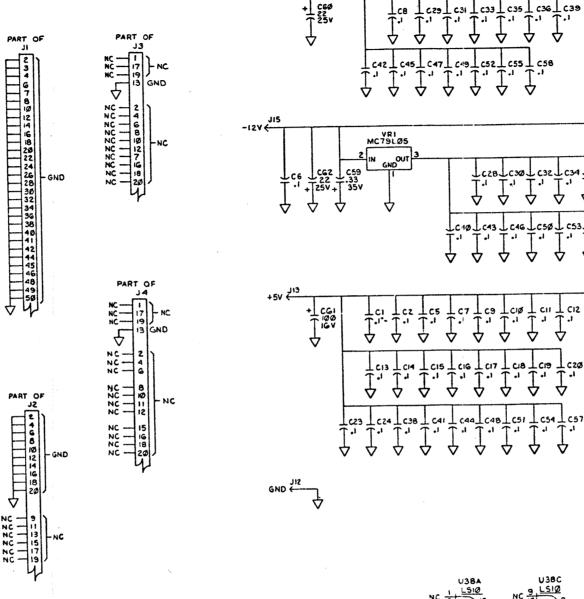

2.2.2.2 Alternate Method - Discrete Wires. If banana plugs are not desired, discrete wires can be used to supply power to the board. Wires can be soldered to the lugs supplied with the banana jacks (Figure 2-2) or four small holes are provided to solder discrete wires to the board. These holes (designated Jl2, Jl3, Jl4, Jl5) are shown in Figure 2-3, and interconnect supply voltages as follows:

| HOLE DESIGNATION | VOLTAGE |

|------------------|---------|

| J12              | Ground  |

| J13              | +5 Vdc  |

| J14              | +12 Vdc |

| <b>J</b> 15      | -12 Vdc |

#### NOTE

Use of the banana jack solder lugs is recommended because of greater mechanical strength and to prevent possible damage to the board.

FIGURE 2-3. Detail Showing Location of Holes J12, J13, J14, J15 to Connect Discrete Power Wires

# 2.2.3 Checking System Clock Jumper

Referring to Figure 2-1, a 2-pin header designated J6 should have a plastic jumper cap in place on it (as shipped). If not, one of the jumpers supplied with the board should be put in place. This jumper connects the system clock source.

# 2.2.4 Selecting Terminal Baud Rate

1

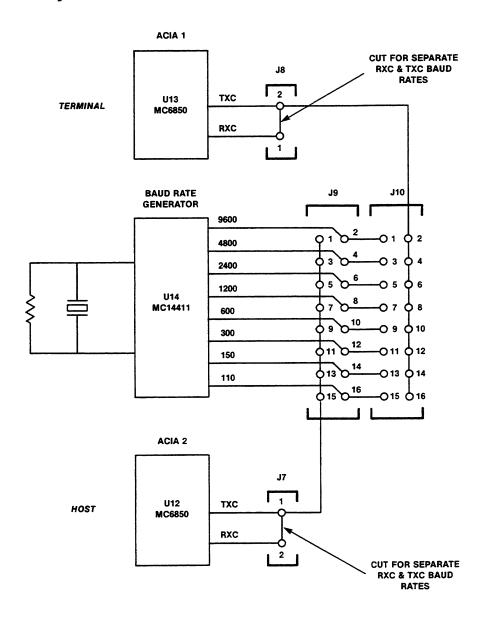

2.2.4.1 Normal Operation - Transmitting and Receiving at the Same Baud Rate. Normally, the terminal transmits and receives at the same baud rate. Although the terminal Port 1 can be configured to transmit and receive at different rates, the board as supplied uses a single common baud rate for the port. The host interface Port 2 has similar attributes. The interconnection circuit is shown in Figure 2-4.

FIGURE 2-4. Interconnection Diagram for Baud Rate Selection

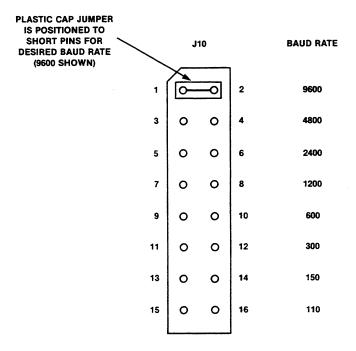

Referring again to Figure 2-1, two headers marked J9 and J10 are shown. Each header consists of a double row of eight pins (16 total), and is used to select the baud rate for a serial port. Header J10 is used to select the terminal baud rate (ACIA 1, serial Port 1).

The pins are jumpered together using a plastic jumper cap (one of seven provided with the board). The cap should be positioned on header J10, as shown in Figure 2-5, to select the desired baud rate. Table 2-1 lists which pins must be jumpered for a given baud rate.

TABLE 2-1. Headers J9 and J10 Jumpers to Select Serial Port Baud Rates

| JUMPER PINS     | SELECTED BAUD RATE |

|-----------------|--------------------|

| 1-2             | 9600               |

| 3-4             | 4800               |

| 5 <del></del> 6 | 2400               |

| 7–8             | 1200               |

| 9-10            | 600                |

| 11-12           | 300                |

| 13-14           | 150                |

| 15-16           | 110                |

|                 |                    |

FIGURE 2-5. Terminal Baud Rate Select Jumper (J10)

Figure 6-4 is a functional schematic diagram of the serial communication ports. The RS-232C signal lines required at each port are shown.

Port 1 must receive an active level on DTR (data terminal ready), or data will not be transmitted. The terminal connected to Port 1 must drive DTR. CTS (clear to send), DSR (data set ready), and DCD (data carrier detect) are each asserted when DTR is asserted. Refer to Appendix C for further information.

- 2.2.4.2 Special Operation Transmitting and Receiving at Different Baud Rates. The MEX68KECB is wired with the transmit clock (TXC) and Receive clock (RXC) of each ACIA (refer to Figure 2-4) tied together and then jumpered to the selected baud rate. To provide different baud rates, the connection between TXC and RXC must be cut and individual baud rates connected to each. Perform the following steps to select separate transmit and receive baud rates for the terminal:

- a. Cut the signal trace located between Pin 1 and Pin 2 of header J8 on the back side of the printed circuit board. BE CAREFUL be sure to cut the correct trace; it is approximately 1/8 inch long.

- b. The transmit baud rate (TXC) is selected by using the plastic jumper cap on header J10 in accordance with Table 2-1.

- c. The receiver baud rate (RXC) is selected by wire-wrapping Pin 1 of header J8 to the desired odd numbered pin of header J10. Again, use Table 2-1 to determine the correct pin.

#### NOTE

The MEX68KECB as now configured is ready to be connected to a terminal and power supplies. If the user wants to utilize options of the printer, tape recorder, and/or host computer (serial Port 2), additional preparation is required. See the appropriate section in this chapter on each option.

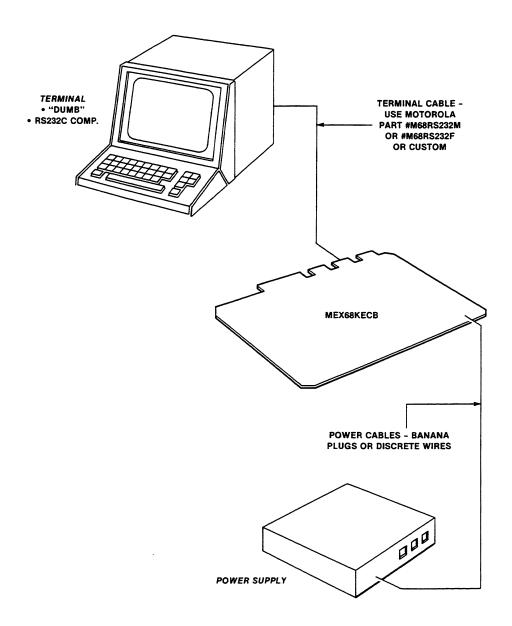

# 2.3 SYSTEM HOOKUP INSTRUCTIONS

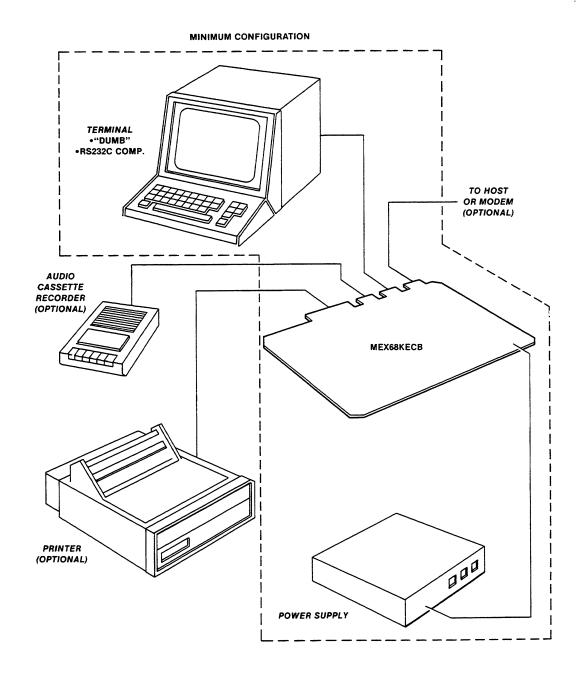

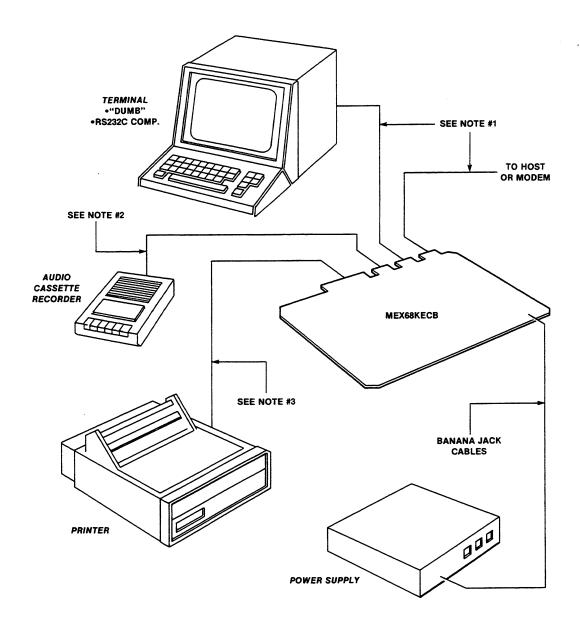

As previously stated, the most simple configuration requires only the MEX68KECB, a terminal, and power supplies (Figure 2-6.) This section describes the required interconnections to hook up this configuration.

FIGURE 2-6. Minimum System Configuration

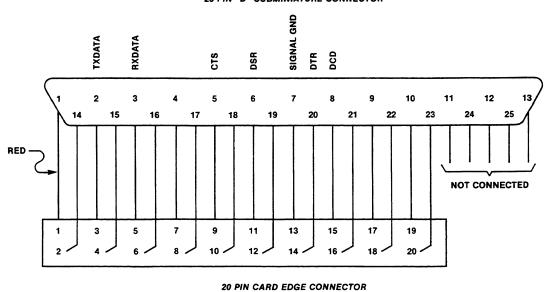

25 PIN "D" SUBMINIATURE CONNECTOR

FIGURE 2-7. Terminal Cable Detail and Signal Line Connections

#### 2.3.1 Connecting the Terminal

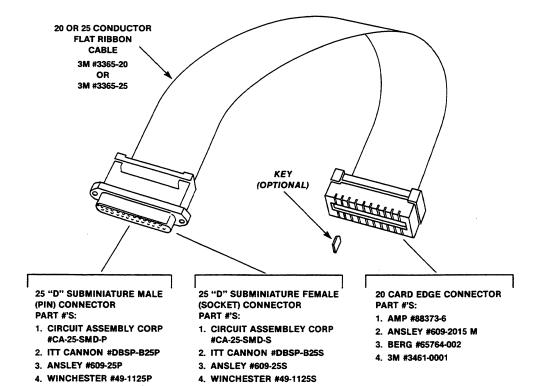

The terminal is connected to the MEX68KECB with a cable (normally flat ribbon) requiring a 20-contact card edge connector on the MEX68KECB end and a 25-contact "D" subminiature connector on the terminal end. The "D" subminiature connector can be either pin (male) or socket (female), as required by the user terminal. Both of these cable types are available from Motorola:

| PART NUMBER | DESCRIPTION                                             |  |  |

|-------------|---------------------------------------------------------|--|--|

| M68RS232M   | RS232 CABLE - Card edge connector/Male DB25 connector   |  |  |

| M68RS232F   | RS232 CABLE - Card edge connector/Female DB25 connector |  |  |

As an alternative, the user can manufacture his own cable. Figure 2-7 shows a detail of the cable, lists several suitable vendor part numbers (any equivalent part can be used), and shows the conductor line designations. The cable requires a 25-conductor flat ribbon; connectors should be installed according to manufacturer's directions. Also, the card edge connector can be keyed to prevent incorrect cable connection.

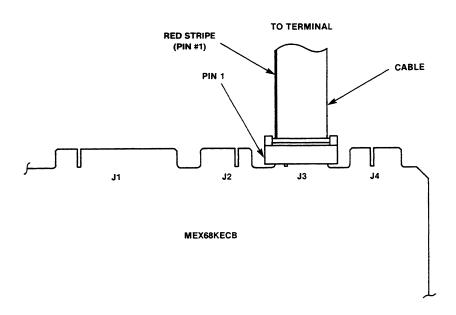

The suitable cable is connected to Port 1 (connector J3), as shown in Figure 2-8, with the other end going to the terminal.

FIGURE 2-8. Terminal Cable Connection to MEX68KECB

# 2.3.2 Connecting the Power Supplies

Three supply voltages are required for the board — that is,  $+5.0 \text{ Vdc} \pm 5$ ,  $+12.0 \text{ Vdc} \pm 10$ , and  $-12.0 \text{ Vdc} \pm 10$ . If the banana jacks are used, cables with standard banana plugs are required to connect the power supplies. With discrete wires, the wires are connected directly to the suitable voltages.

All supply voltages must be referenced to ground, and these connections should be made before turning on power. The voltage turn-on must be done in proper sequence to prevent damage to the RAM devices. Follow system turn-on instructions in the following section.

### 2.4 SYSTEM TURN-ON AND INITIAL OPERATION

### CAUTION

POWER SUPPLY VOLTAGES MUST BE TURNED ON IN PROPER SEQUENCE TO AVOID DAMAGE TO THE DYNAMIC RAM DEVICES. FOLLOW THE TURN-ON INSTRUCTIONS TO PREVENT PROBLEMS.

After the cables are in place, the final step to system turn-on is applying power. The dynamic RAM devices (MCM4116's) require that the negative voltage -12 Vdc be applied first. This is especially important when individual power supplies (such as laboratory supplies) are used. The power-up sequence should be:

- a. Ground must be connected common to all power supplies.

- b. Turn on -12.0 Vdc.

- c. Turn on +12.0 Vdc.

- d. Turn on +5.0 Vdc.

If a single multivoltage power supply is used, it is not possible to turn voltages on independently. However, with most power supplies the -12 Vdc and +12 Vdc come up before the +5 Vdc because these are lightly loaded and do not have to charge heavy internal filter capacitance. The user should test the multivoltage supply, simulating typical loading from Table 1-1, to determine if the -12 Vdc comes up first. When powering up with a single multivoltage supply:

- a. Be sure all voltages are connected prior to power up.

- b. Turn power ON to the board.

### CAUTION

THE POWER DOWN SEQUENCE IS THE REVERSE OF THE ABOVE POWER UP SEQUENCE AND IS EQUALLY IMPORTANT.

After power on, the system should initialize itself and print on the terminal:

NOTES: 1. USE MOTOROLA CABLE M68RS232M OR M68RS232F OR MAKE CUSTOM.

- 2. MAKE CUSTOM CABLE.

- 3. USE MOTOROLA CABLE MEX68PIC OR MAKE CUSTOM.

FIGURE 2-9. Expanded System Configuration with Options

It is now ready for operation under control of the firmware as described in Chapters 3 and 4. If this response does not appear on the terminal, perform the following system checks:

- a. Press the black reset button to guarantee that the board has been initialized properly.

- b. Check that the terminal and board are set for the same baud rates.

- c. If the baud rates are set properly and the terminal is still not reacting properly, the terminal may require special null characters and formatting from the educational computer. The Port Format (PF) command can be used to set the required ACIA format (see Paragraph 3.5.21 and Appendix B).

### 2.5 PREPARATION FOR USE OF SYSTEM OPTIONS

The MC68000 Educational Computer Board can use options of a Centronics-compatible printer, audio cassette storage, and a link to a host computer. Figure 2-9 shows the expanded system configuration with these options. The following paragraphs describe preparation for use of each option.

### 2.5.1 Printer Option

The board is properly buffered to directly drive a Centronics-compatible printer. The Port 3 edge connector Jl must be connected via cable to the user-supplied printer. This cable is available from Motorola, Part Number MEX68PIC.

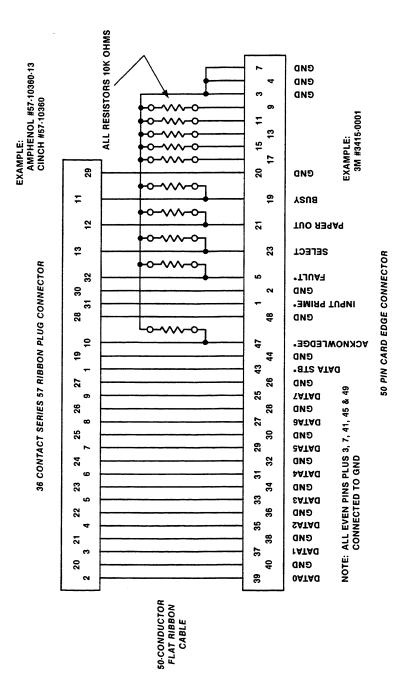

The user may desire to manufacture this cable, although it is a more complex assembly than just flat ribbon cable and connectors. Resistors are used on the cable to help protect unbuffered inputs from damage due to static discharge. Figure 2-10 shows the interconnection diagram of the cable and lists suitable connector part numbers. Note that the cable can be keyed on the card edge connector to prevent incorrect cable connection.

FIGURE 2-10. Printer Cable Interconnection Diagram

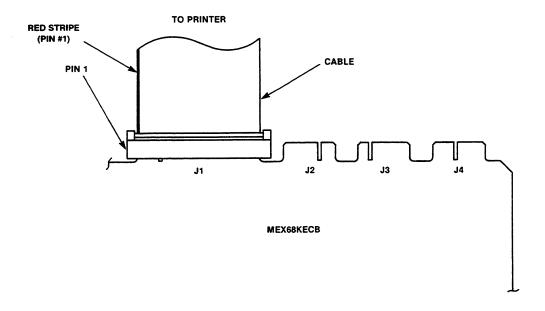

The cable is connected to Port 3 (connector J1), as shown in Figure 2-11, with the other end going to the printer.

FIGURE 2-11. Printer Cable Connection to MEX68KECB

## 2.5.2 Host Computer (Modem) Option

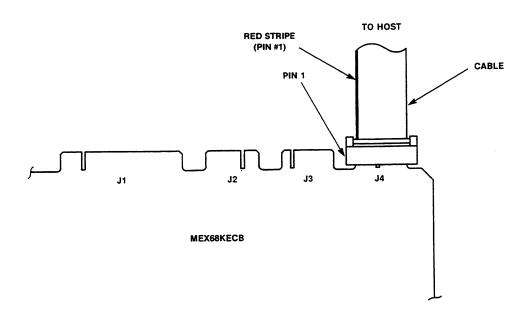

A second serial RS-232 port, Port 2 connector J4, is provided to interconnect into a host computer directly or by modem. Preparation similar to serial Port 1 is required — that is, program the baud rate and prepare a cable.

Again referring to Figure 6-4, the modem or host connected to Port 2 must assert CTS (clear to send) before information can be transmitted via Port 2. RTS is asserted by the ECB when power is applied to the board. DTR is asserted as part of the ECB power-up/reset firmware.

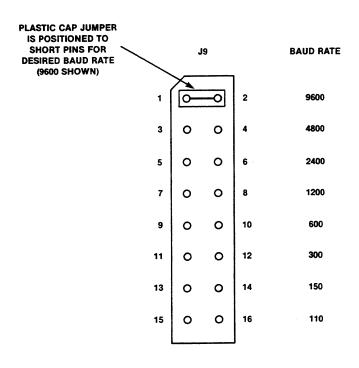

2.5.2.1 <u>Selecting Host Baud Rate</u>. As with the terminal baud rate, the host serial port is wired to transmit and receive at the <u>same</u> baud rate. The desired baud rate is selected via a plastic cap jumper positioned on header J9, as shown in Figure 2-12. Also reference Figure 2-4 for the interconnection diagram and Table 2-1 for the selected baud rate.

FIGURE 2-12. Host Baud Rate Select Jumper (J9)

Again similar to the terminal port, to provide <u>different</u> baud rates, the connection between TXC and RXC for ACIA2 must be cut (reference Figure 2-4) and individual baud rates connected to each. Perform the following steps to select separate transmit and receive baud rates for the host port:

- a. Cut the signal trace located between Pin 1 and Pin 2 of header <u>J7</u> on the back side of the printed circuit board. BE CAREFUL be sure to cut the correct trace; it is approximately 1/8 inch long.

- b. The transmit baud rate (TXC) is selected by using the plastic jumper cap on header J9 in accordance with Table 2-1.

- c. The receiver baud rate (RXC) is selected by wire-wrapping <u>Pin 2 of header J7</u> to the desired <u>even numbered pin of header J9</u>. Again, use Table 2-1 to determine the correct pin.